## Kapitel 4 Grundlagen zur Parallelverarbeitung

**SWT I – Sommersemester 2009**

Prof. Dr. Walter F. Tichy

Dipl.-Inform. David J. Meder

## Warum Parallelverarbeitung?

- Anwendungen brauchen mehr Leistung oder mehr Ressourcen als Ein-Prozessorsysteme bieten können.

- Warten auf nächste Hardware-Generation hilft nicht mehr, denn Taktfrequenzen steigen kaum noch, Parallelität auf Instruktionsebene ist ausgeschöpft.

- "Grand-Challenge" Applikationen aus Chemie, Astronomie, Bioinformatik, CAD/CAM, ...

[Linux-Magazin.com]

Simulationen, wenn Experimente unmöglich sind

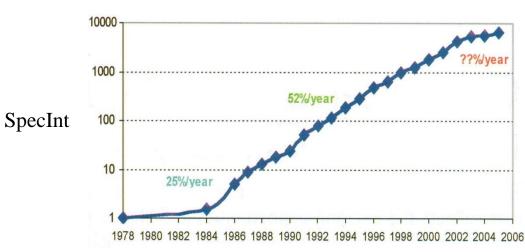

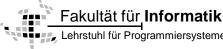

## Moore's Law

- Moore, G.E.:

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year." (1965)

- Moore, G.E.:

"The new slope might approximate a doubling every two years, rather than every year, by the end of the decade."

(1975)

Quelle: http://www.intel.com/technology/mooreslaw/

# David Patterson, Präsident ACM:

"In case you weren't paying attention, the era of doubling performance every 18 months ended in 2002."

President's Letter, Comm of ACM, März 2006

## 0

### Was ist passiert?

## Strategische Änderung: Multiprozessoren auf einem Chip

Hersteller haben eine kritische Schwelle überschritten: Mehrere Prozessorkerne pro Chip sind möglich und preiswert:

| Hersteller | #Kerne/Chip | etwa seit |

|------------|-------------|-----------|

| IBM        | 2           | 2004      |

| IBM        | 9           | 2005      |

| AMD        | 2           | 2005      |

| AMD        | 4           | 2007      |

| Intel      | 2           | 2006      |

| Intel      | 4           | 2007      |

| Intel      | 6           | 2008      |

| SUN        | 8           | 2005      |

- Wachsende Anzahl von Prozessorkernen pro Chip sind prognostiziert (wegen weiterem Schrumpfen der Abmessungen der Transistoren, Leitungen, etc.)

- Intel stellte 2006 einen Prototypen mit 80 Prozessoren auf einem Chip vor

## Ihr Laptop – ein Parallelrechner?

Stand: Juni 2007

#### Inspiron<sup>TM</sup> 6400

15" Notebook für vielseitige Unterhaltung & 1 GB RAM.

#### <del>729 €</del>

659 €

inkl. MwSt., zzgl. 78 € Versand

#### Prozessor

Intel® Pentium® Dual-Core T2080 Prozessor (1,73 GHz, 533 MHz, 1 MB L2-Cache)

### Inspiron<sup>TM</sup> 1520

Stylischer Denker, der es geniesst seine Qualitäten zeigen zu können und gerne im Mittelpunkt steht.

#### 999 €

899 €

inkl. MwSt., zzgl. 78 € Versand

#### Prozessor

Intel® Core <sup>™</sup> 2 Duo T5450 Prozessor (1,66 GHz, 667 MHz, 2 MB L2-Cache)

#### Inspiron<sup>TM</sup> 1720

Unterhaltung & Spaß garantiert! Technologie genau angepasst für Ihren Lifestyle. Jetzt in 8 Farben.

#### 1.049 €

inkl. MwSt. und Versand

#### Prozessor

Intel® Core <sup>™</sup> 2 Duo T5250 Prozessor (1,5 GHz, 667 MHz, 2 MB L2-Cache)

#### Inspiron<sup>TM</sup> 1520

Schlank, elegant und noch etwas schlauer und stärker. Jetzt in 8 Farben.

#### <del>1.129 €</del>

1.079 €

inkl. MwSt., zzgl. 78 € Versand

#### Prozessor

Intel® Core <sup>™</sup> 2 Duo T7100 Prozessor (1,8 GHz, 800 MHz, 2 MB L2-Cache)

7

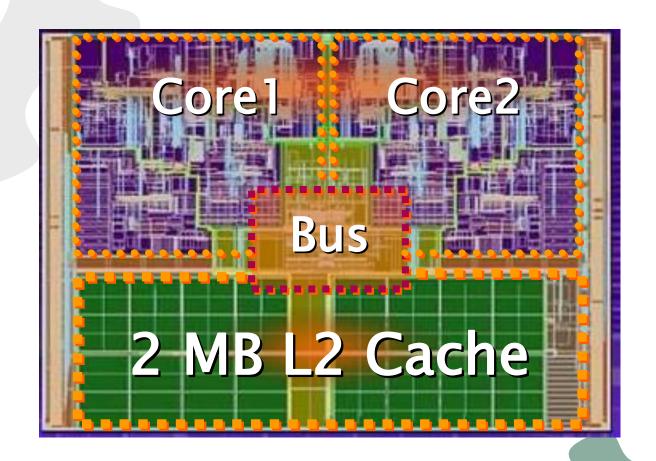

### **Doppelprozessor Intel Core Duo**

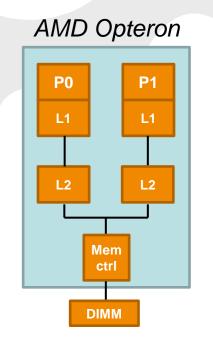

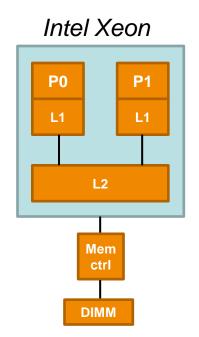

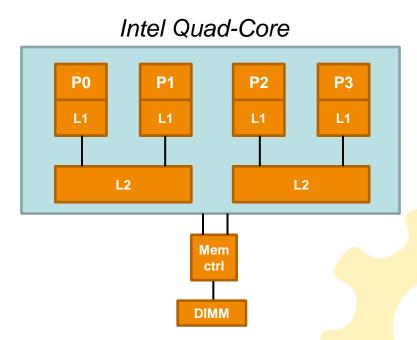

## Mehrkern-Architekturen(2)

### **Dual-Core und Quad-Core**

Mehrere Prozessoren pro Chip

Getrennte L1/L2-Caches, was zu divergenten Kopien der gleichen Variablen führt. Cache-Kohärenz nur bei bestimmten Ereignissen,

z.B. beim Schreiben in den Speicher.

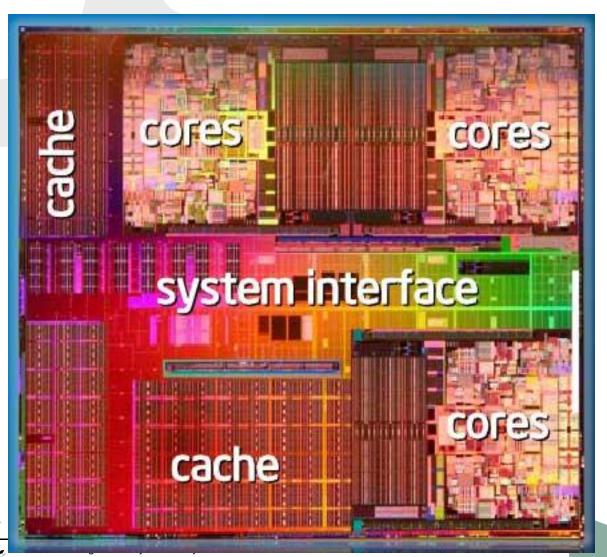

# Intel Dunnington 6 Prozessoren auf einem Chip

3 x 2 Xeon Prozessoren

(nicht HWmehrfädig)

2,6 GHz

130 W

45nm Technik

Lieferbar 2008

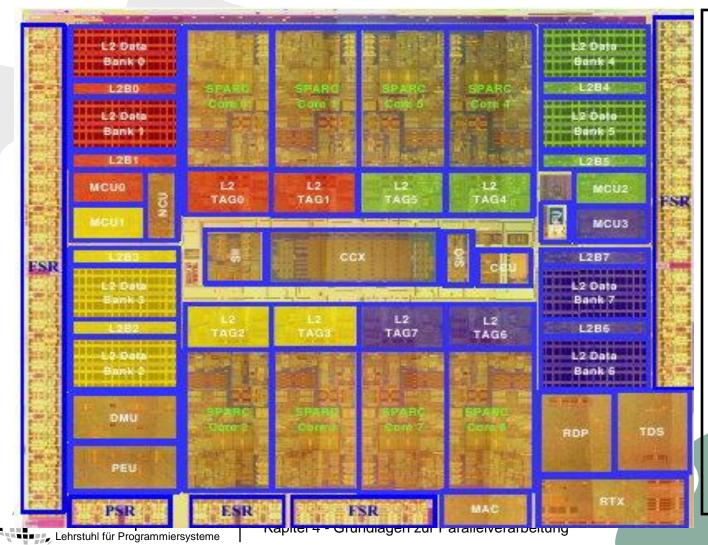

## Sun Niagara 2: 8 Prozessoren auf 3,42 cm<sup>2</sup>

8 Sparc Prozessoren

8 HW-Fäden pro Prozessor

8x9 Kreuzschiene

1,4 GHz

**75 W**

65nm Technik

Lieferbar 2007

**Erste Version 2005**

11

## 0

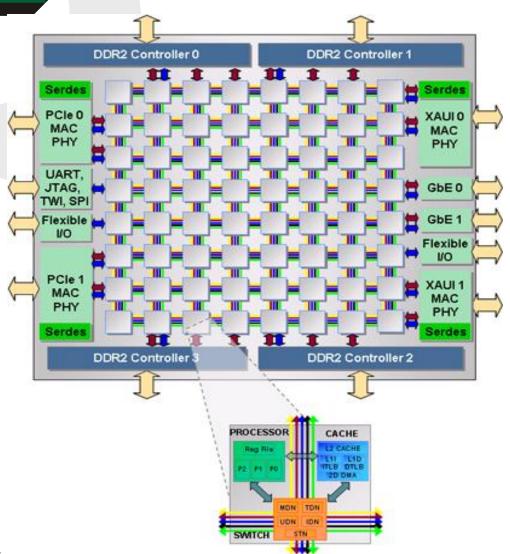

### Tilera's TILE64

64 VLIW Prozessoren plus Gitter auf einem Chip

Für eingebettete Anwendungen (Netz- und Videoanwendungen)

700 MHz

**22 W**

Lieferbar 2007

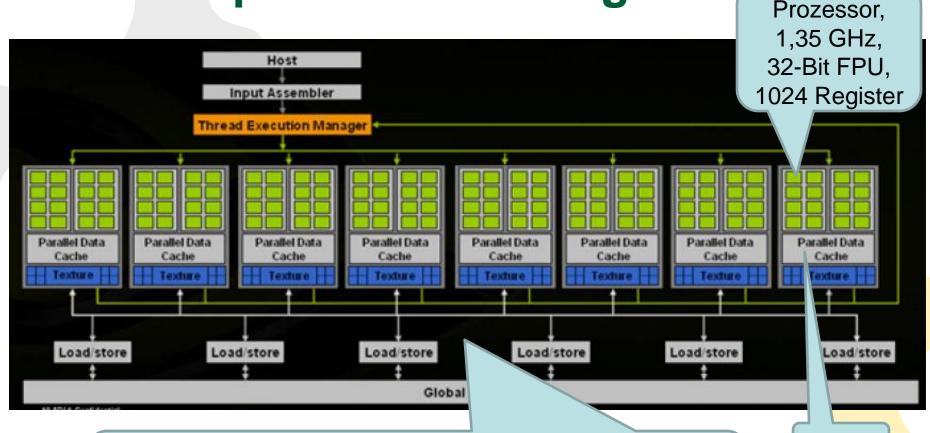

Nvidia GeForce 8

Graphics Processing Unit

128 Prozessoren insgesamt, jeder mit 96 Fäden in HW Insgesamt 12288 HW-Fäden! SIMD, gemeinsamer und verteilter Speicher

Fakultat rur intormatik

Lehrstuhl für Programmiersysteme

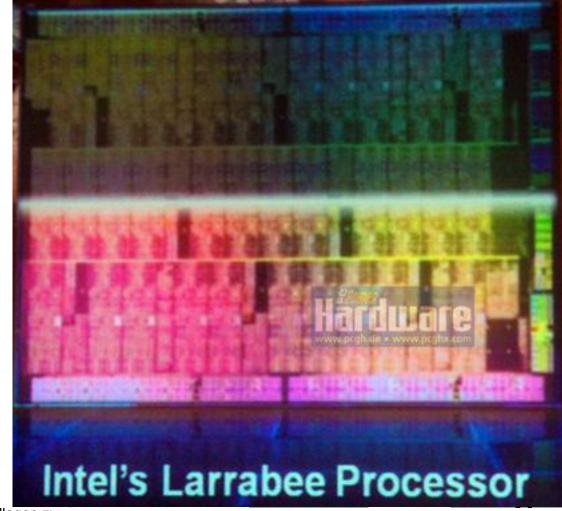

# Intels Larrabee: 32 bis48 Pentium-Kerne auf einem Chip

- 32 x86 Prozessoren (45nm),

- 48 x86 Prozessoren (32 nm)

- Cache-kohärent,

- Ring-Verbindung

- 64-BitArithmetik

- 4 Fäden pro Prozessor

- Vektor-Befehle für Grafik

- Erwartet 2010

Kapitel 4 - Grundlagen zı

Quelle: www.pcgameshardware.com, May 12, 2009

## Moore'sche Regel, neue Version

Verdopplung der Anzahl

Prozessoren pro Chip

mit jeder Chip-Generation,

bei etwa gleicher Taktfrequenz

Parallelrechner werden in naher Zukunft flächendeckend zur Verfügung stehen.

## Was sind die Folgen? (1)

- Hauptproduktlinie der Prozessor-Hersteller sind Multikern-Chips.

- Server werden bereits seit 2005 mit Multikern-Chips ausgeliefert.

- Sogar Laptops werden seit 2006 mit Doppelprozessor-Chips ausgestattet (Dell, Apple, u.s.w.)

## Was sind die Folgen? (2)

- Leistungssteigerungen von alltäglichen Anwendungen wird durch Parallelisierung erreicht.

- Parallelismus wird zum Normalfall.

- Informatiker müssen Parallelismus beherrschen lernen.

- Fundamentaler Übergang vom sequentiellen zum parallelen Rechnen auf breiter Front mit dramatischen Auswirkungen auf Anwendungen, Forschung, und Lehre.

## Was sind die Folgen? (3)

- Die Softwarehersteller und die Informatikausbildung müssen rasch auf Parallelverarbeitung umstellen, um Wettbewerbsfähigkeit zu erhalten.

- Umstellung von existierenden Anwendungen

- Erstellung neuer, paralleler Anwendungen

## GRUNDLAGEN PARALLELVERARBEITUNG

# Programmieransätze & Terminologie

Def.: parallel [griechisch]

Allgemein: nebeneinander verlaufend, in gleichem Abstand [Brockhaus]

Informatik: gleichzeitig ablaufend

Anmerkung: In der Informatik-Literatur wird manchmal zwischen "nebenläufig" (im Sinne von "nicht kausal von einander abhängig") und "parallel" (im Sinne von "simultan") unterschieden. Diese Unterscheidung werden wir an keiner Stelle brauchen und verwenden daher beide Begriffe synonym.

# Programmieransätze & Terminologie: Überblick

- Grundsätzlich zwei wichtige Programmieransätze

- Für Parallelrechner mit gemeinsamem Speicher

- Prozesse und Kontrollfäden (engl. Threads)

- z.B. Anwendung bei Multikernrechnern

- Für Parallelrechner mit <u>verteiltem Speicher</u>

- Nachrichtenaustausch (engl. Message Passing)

- z.B. Anwendung bei Rechnerbündel

- Wird in dieser Vorlesung nicht weiter behandelt.

## Programmieransätze & Terminologie: gemeinsamer Speicher (1)

### **Prozess**

- Wird durch Betriebssystem erzeugt

- Enthält Informationen über Programmressourcen und Ausführungszustand, z.B.

- Code-Segment (Programminstruktionen)

- Daten-Segment (für globale Variablen, Halde)

- Mind. 1 Kontrollfaden

- CPU-Kontextwechsel zwischen Prozessen langsam

### Kontrollfaden

- Unabhängiger Instruktionsstrom, der ausgeführt werden kann

- Existiert in einem Prozess

- Ein Faden hat eigenen

- Befehlszeiger

- Keller

- Register-Kopien

- Teilt sich mit anderen Fäden

- Adressraum

- Code/Daten-Segment

- Andere Ressourcen (z.B. geöffnete Dateien, Sperren, etc.)

- CPU-Kontextwechsel zw. Fäden des gleichen Prozesses schneller

## Programmieransätze & Terminologie: gemeinsamer Speicher (2)

- Prinzipielles Vorgehen bei gemeinsamen Speicher

- Fäden enthalten parallel auszuführende Aufgaben (Instruktionen)

- Informationsaustausch über gemeinsam genutzte Variablen im Speicher

- Synchronisationskonstrukte koordinieren Ausführung im Falle von Daten- oder Kontrollabhängigkeiten

- Fäden werden grundsätzlich vom Betriebssystem erzeugt und auf Prozessoren bzw. Kerne verteilt

- Schnittstelle dazu meist in Programmiersprachen eingebaut (z.B. Java Threads) oder über Bibliotheken.