Prof. Dr.-Ing. Dr. h. c. J. Becker

becker@kit.edu

Karlsruher Institut für Technologie (KIT)

Institut für Technik der Informationsverarbeitung (ITIV)

# Digitaltechnik

Einführung in CMOS-Technologie

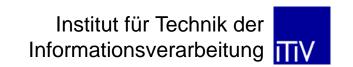

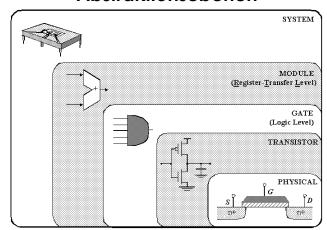

# **Entwurfsraum - Abstraktionsebenen**

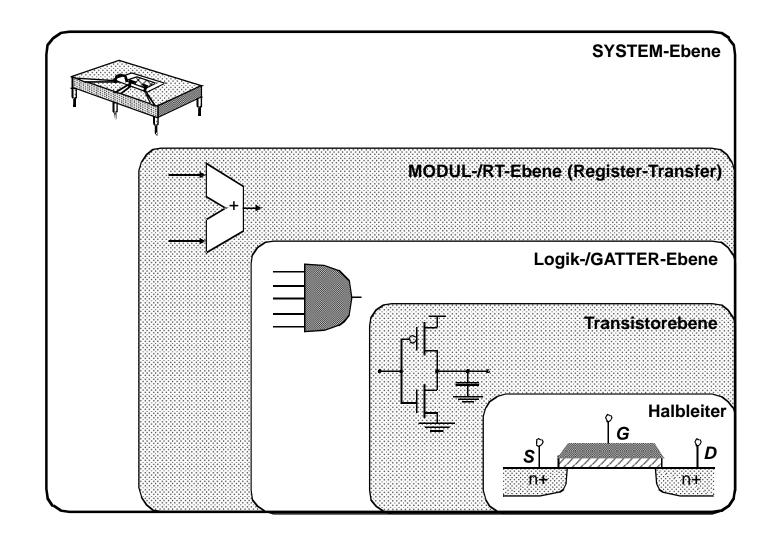

# Planartechnik – PN-Übergang

- <u>Diffusion:</u> Sowohl Elektronen als auch Löcher wandern in die p- bzw. n-Gebiete

- <u>Drift:</u> durch das Wandern der Ladungen entsteht ein Elektrisches Feld welches der Diffusion entgegenwirkt -> <u>Gleichgewicht</u> zwischen <u>Diffusion</u> und <u>Drift</u> entsteht

# Planartechnik – PN-Übergang

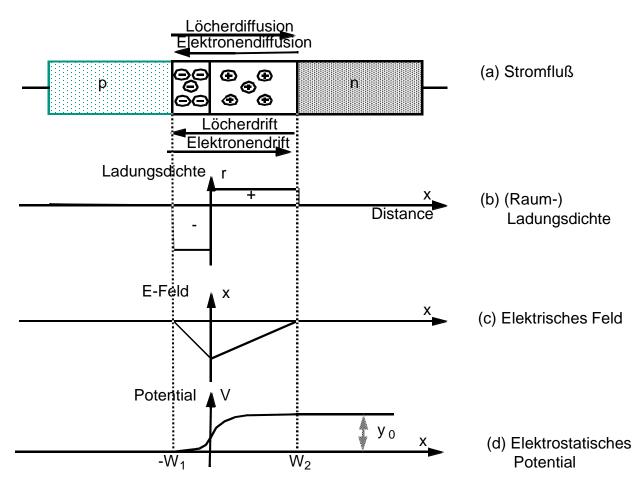

- a) **Sperrschichtpolung:** negativer Pol ans p-Gebiet, positiver Pol ans n-Gebiet

- → Raumladungszonen werden vergrößert

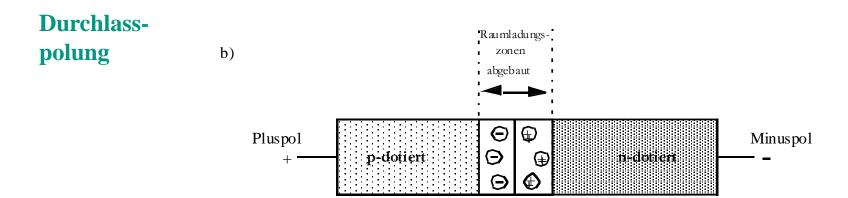

- b) <u>Durchlasspolung:</u> positiver Pol ans p-Gebiet, negativer Pol ans n-Gebiet

- → Raumladungszonen werden verkleinert

- → Ladungsträgerbewegung über die Grenzschicht

# **Aufbau einer Diode**

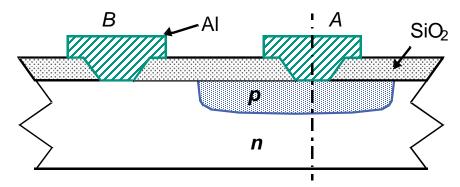

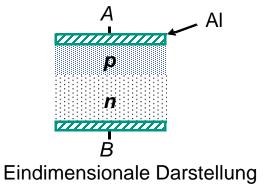

Querschnitt eines pn-Kontaktes in einem IC-Prozess

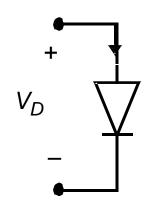

$$I_D = I_S(e^{V_D/f}T - 1)$$

Diodensymbol

- Diode ermöglicht nur einen Stromfluss von p nach n, d.h. von Anschluss A nach B

- Die Gleichung I<sub>D</sub> beschreibt das Strom-/Spannungsverhalten der Diode in Abhängigkeit von V<sub>D</sub>

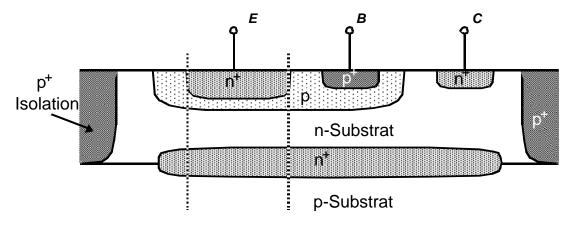

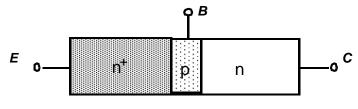

# **Aufbau eines Bipolar-Transistor**

(a) Querschnittdarstellung.

- (b) Idealisierte Darstellung.

- Bipolar-Transistoren werden oft in Analogschaltungen eingesetzt, z.B. Hifi-Verstärker

- Anordnung von 3 dotierten Gebieten

- -> Folge pnp oder npn, wobei die mittlere Schicht sehr dünn ausgelegt wird

- Im Gegensatz zu MOS-Transistoren sind beim **Bipolar-Transistor** sowohl *Majoritäts*-als auch *Minoritätsladungsträger* beim Stromfluss beteiligt

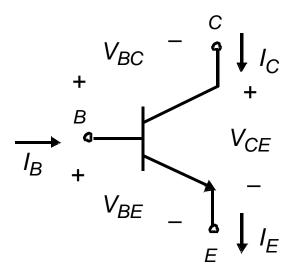

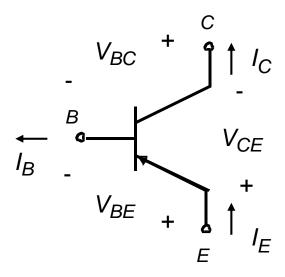

# **Bipolar-Transistor**

### **Schaltsymbole und Vorzeichen-Konventionen:**

(a) npn

(b) pnp

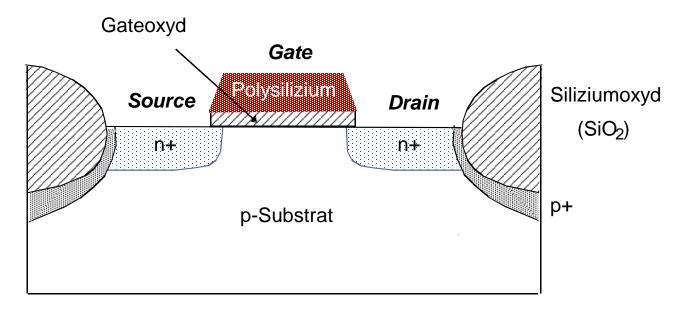

## Aufbau eines MOS-Feldeffekttransistors

### **Querschnitt eines NMOS-Transistors:**

- MOS-FETs werden meist in Digitalschaltungen eingesetzt

- Der Strom durch den MOS-FET fließt in lateraler Richtung

- Am Stromfluss sind ausschließlich Majoritätsladungsträger beteiligt

- Das Gate dient als Schalter -> aktiviert den Kanal zwischen Source und Drain

-> angelegte positive Spannung: zieht Elektronen an und verdrängt Löcher

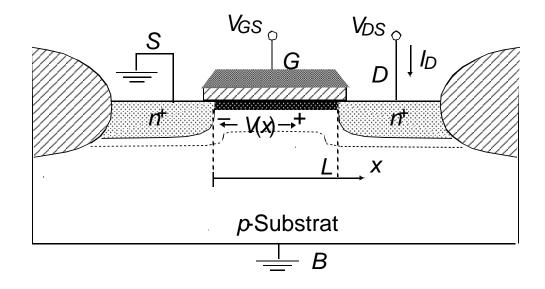

# **MOS-Technologie**

### Strom-Spannungszusammenhang -> Durchlassspannung

- Transistor ist gesperrt: d.h. V<sub>GS</sub>< V<sub>th</sub>, somit kann zwischen Source und Drain der Strom I<sub>D</sub> nicht fließen

- Transistor ist geöffnet: d.h. V<sub>GS</sub>> V<sub>th</sub>, zwischen Source und Drain Gebieten bildet sich eine negative Ladungszone

- → Stromfluss zwischen Source und Drain ermöglicht

### **Der MOS-Transistor**

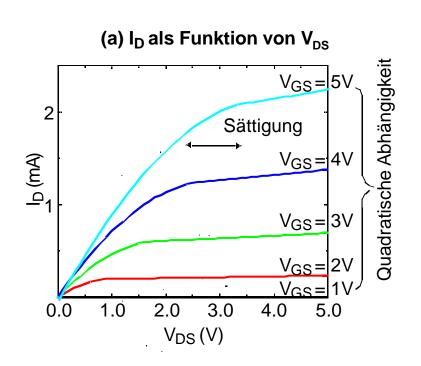

### I-V Zusammenhang

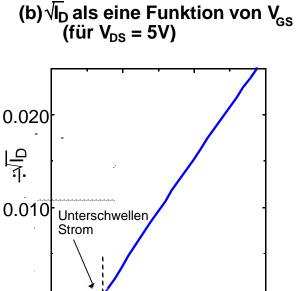

0.0

- Damit der Stromfluss I<sub>D</sub> zustande kommt, muss die Ansteuerspannung V<sub>GS</sub> den Wert V<sub>⊤</sub> überschreiten (rechtes Diagramm)

- Ist die Ansteuerspannung V<sub>GS</sub> größer V<sub>T</sub> und konstant:

- → Strom I<sub>D</sub> ist nur noch von V<sub>DS</sub> abhängig (linkes Diagramm)

2.0

3.0

### **Der MOS-Transistor**

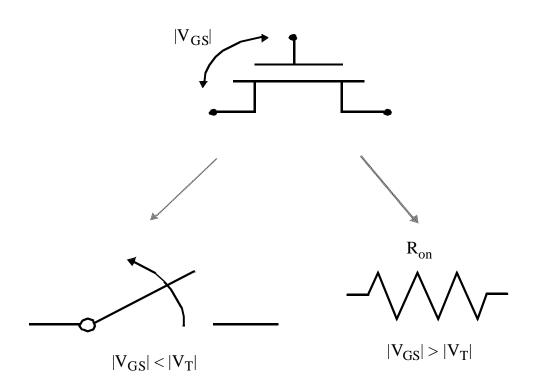

### **Schaltmodell:**

- Im nichtleitenden Zustand, d.h.  $|V_{GS}| < |V_T|$  gilt: MOS-Transistor wird zu einem geöffneten Schalter  $\rightarrow$  Widerstand mit sehr hoher Impedanz, der Stromfluss behindert

- Im **leitenden Zustand**, d.h.  $|V_{GS}| > |V_T|$  gilt: MOS-Transistor wird zu einem Widerstand mit einer sehr geringen Impedanz, der Stromfluss verstärkt (geschlossener Schalter)

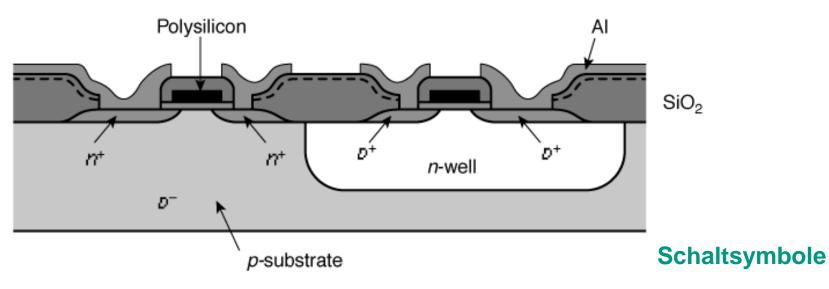

# **MOS-Technologie**

### **Querschnitt der CMOS-Materialschichten (Complementary MOS)**

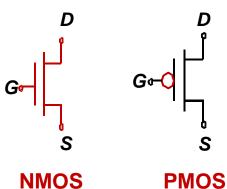

- Man unterscheiden zwei grundsätzliche MOS-Transistortypen → NMOS- und PMOS-Transistoren

- In der Abbildung: NMOS oben links, PMOS oben rechts

- In der CMOS-Technologie werden beide Typen in jeweils komplementären Netzen eingesetzt

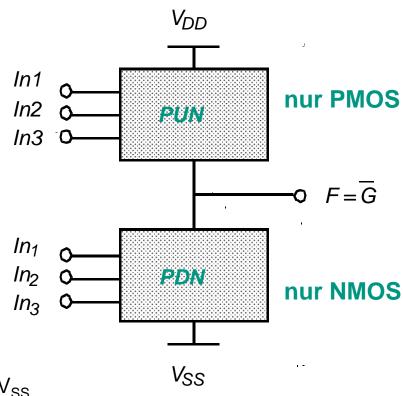

# Struktur einer statischen CMOS-Schaltung

### **PUN und PDN -> duale (komplementäre) Netze:**

- Die CMOS-Technologie basiert auf komplementären Netzen

→ PUN und PDN

(Pull-Up/Pull-Down Netz)

- Ist der Ausgang der realisierten Funktion gleich 1, schaltet das PUN-Netz den Ausgang F auf V<sub>DD</sub>

- Ist der Ausgang hingegen gleich 0, schaltet das PDN-Netz den Ausgang F auf V<sub>ss</sub>

- Zur Realisierung der PUN-Netze werden PMOS-Transistoren eingesetzt, PDN-Netze werden mit NMOS-Transistoren implementiert

- Da außer zu Schaltzeitpunkten keine direkte Verbindung zwischen V<sub>DD</sub> und V<sub>SS</sub> besteht, wird während des Haltens sehr wenig Energie verbraucht

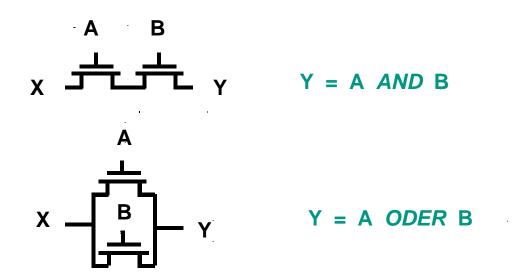

# NMOS-Transistoren in Serien/Parallelschaltung

Transistoren → Schalterrealisierung

→ Steuerung durch Gate-Signal

NMOS-Schalter schließt, wenn das Gate auf "high" (H, "1") ist

# NMOS-Transistoren in Serien/Parallelschaltung

PMOS-Schalter schließt, wenn das Gate auf "low" (L, "0") ist

$$X = A \quad A \quad Y = A \quad AND \quad B = A + A$$

$$Y = A \quad OR \quad B = AB$$

$$X = A \quad OR \quad B = AB$$

NMOS-, PMOS-Schaltungen: Anbindung an Axiome der Schaltalgebra

→ Realisierung der Konjunktion, Disjunktion und Negation

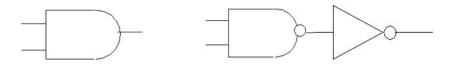

# Konstruktion einer statischen CMOS-Schaltung

**PUN** ist zu **PDN** dual (→ komplementär) (kann mittels DeMorgan`s Theorem gezeigt werden)

$$\overline{A + B} = \overline{A} \overline{B}$$

$$\overline{AB} = \overline{A} + \overline{B}$$

### Das komplementäre Gatter ist invertierend

$$AND = NAND + INV$$

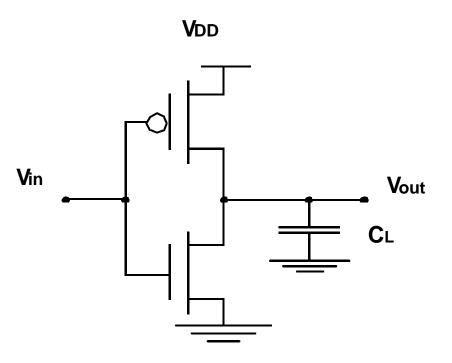

# CMOS: Inverter-Schaltung

- Der Inverter besteht aus zwei Transistoren, einem NMOS und einem PMOS

- Ist Vin auf high, so öffnet der NMOS-Transistor und Vout wird auf GND gezogen, während dessen ist der PMOS-Transistor gesperrt

- Ist V<sub>in</sub> hingegen auf *low*, so öffnet der PMOS-Transistor und V<sub>out</sub> wird auf V<sub>DD</sub> gezogen, der NMOS-Transistor wird hingegen gesperrt

- Strom zwischen VDD und GND kann nur fließen, wenn die Transistoren umschalten und kurzzeitig beide offen sind

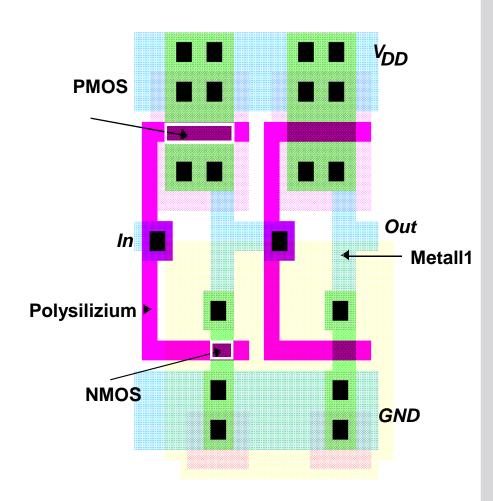

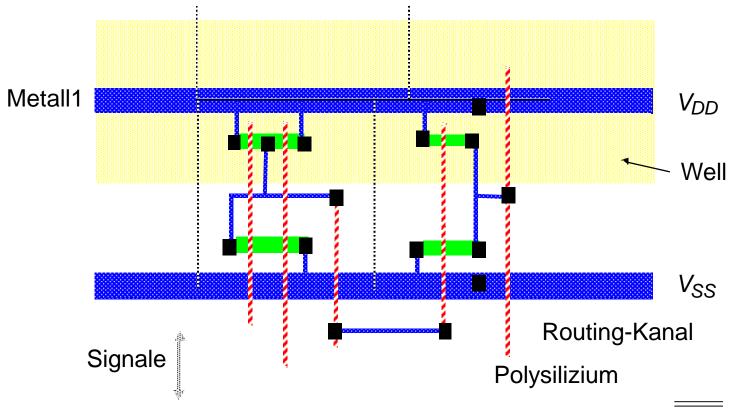

# CMOS: *Inverter*-Layout

- Das Layout stellt zwei in Serie geschaltete Inverter dar

- Das Polysilizium wird genutzt, um die Gates auf dem Silizium zu realisieren

- Das rote Gebiet oben ist die n-Wanne für die PMOS-Transistoren

- Die blauen Felder sind Metalleiter, wo meist Aluminium oder in moderneren Verfahren Kupfer zum Einsatz kommt

- Die grünen Gebiete sind Diffusionsgebiete, und mit schwarzen Vierecken stellen diese Kontaktierungen zwischen den Source- bzw. Drain-Gebieten und den Metalleitern dar

### **CMOS-Maskenlayout**

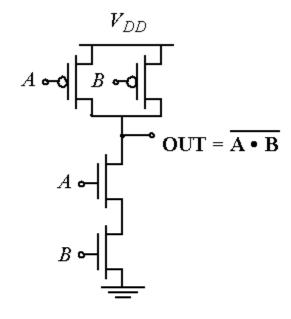

# **CMOS-Beispielgatter:** *NAND*

#### **CMOS-Schaltung für** *NAND*

|                               |   |   |     | _ |  |  |

|-------------------------------|---|---|-----|---|--|--|

|                               | A | В | Out |   |  |  |

|                               | 0 | 0 | 1   |   |  |  |

|                               | 0 | 1 | 1   |   |  |  |

|                               | 1 | 0 | 1   |   |  |  |

|                               | 1 | 1 | 0   |   |  |  |

| Truth Table of a 2 input NAND |   |   |     |   |  |  |

gate

PDN:

$$G = A B \Rightarrow Conduction to GND$$

PUN:

$$F = A + B = AB \Rightarrow$$

Conduction to  $V_{DD}$

$$G(In_1,In_2,In_3,\ldots) \equiv F(\overline{In_1},\overline{In_2},\overline{In_3},\ldots)$$

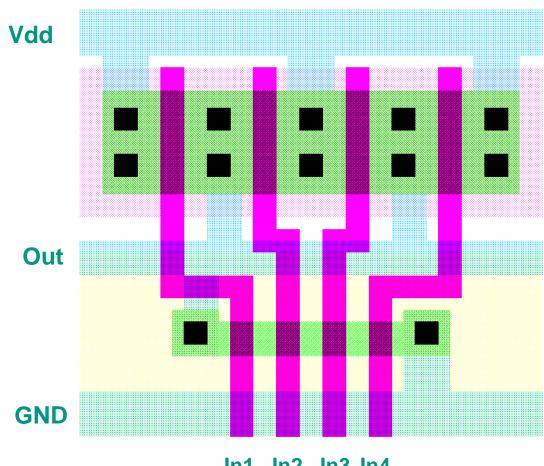

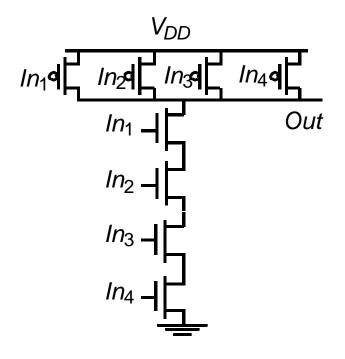

# CMOS: NAND-Gatter mit 4 Eingängen

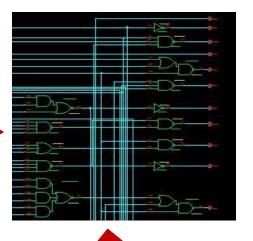

### **CMOS-Maskenlayout**

### **CMOS-Schaltung** für NAND-4

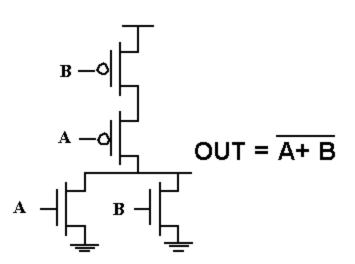

# **CMOS-Beispielgatter:** *NOR*

### **CMOS-Schaltung für** *NOR*

|                                   | A | В | Out |  |  |  |

|-----------------------------------|---|---|-----|--|--|--|

|                                   | 0 | 0 | 1   |  |  |  |

|                                   | 0 | 1 | 0   |  |  |  |

|                                   | 1 | 0 | 0   |  |  |  |

|                                   | 1 | 1 | 0   |  |  |  |

| Truth Table of a 2 input NOR gate |   |   |     |  |  |  |

PUN- und PDN-Netzentwurf (Funktionen G und F zur Übung!)

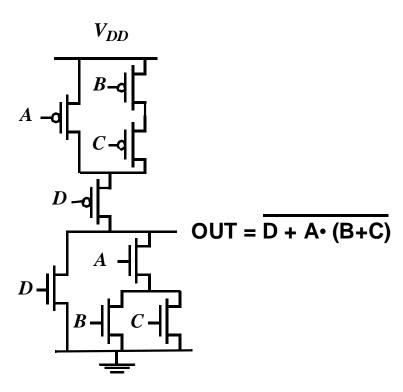

# CMOS-Beispielgatter: komplexes Gatter

CMOS-Schaltung für komplexes Gatter

- In der CMOS-Technik lassen sich ebenfalls komplexere Gatter modellieren (siehe Schaltung oben)

- Dies muss jedoch durch entsprechende *Dimensionierung* der *W* (Transistor-Kanalbreite) und *L* (Kanallänge)

Größen der Transistoren geschehen, damit die geforderte Symmetrie wie beim Inverter erhalten bleibt

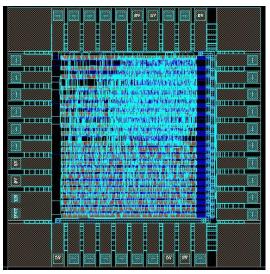

# Standardzellenlayout-Methodik

- Das oben dargestellte **Standardzellenlayout** realisiert die Funktion: y = a & b = a & b

- Die Standardzellen-Methodik beinhaltet nur Basiszellen gleicher Höhe

-> oben VDD- und unten Vss-Leitungen: in den Zwischenräumen werden die gewünschten Schaltglieder (Gatter) modelliert

# Heutiger Rechnergestützter Entwurf

**Synthese**

(Synopsys)

#### Hardware Beschreibung

#### **Netzliste**

#### **Abstraktionsebenen**

# Platzierung & Verdrahtung

(Cadence/ Mentor)

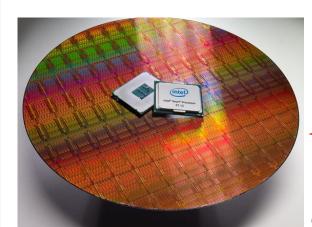

**Fabrikation**

**Chip Wafer**

Masken-Layout

## Status der Mikroelektronikindustrie

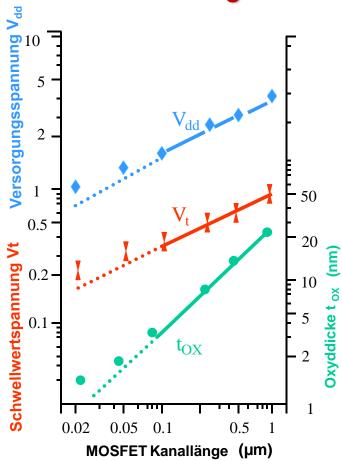

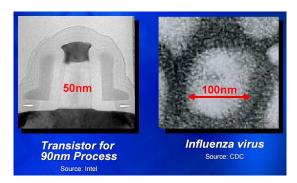

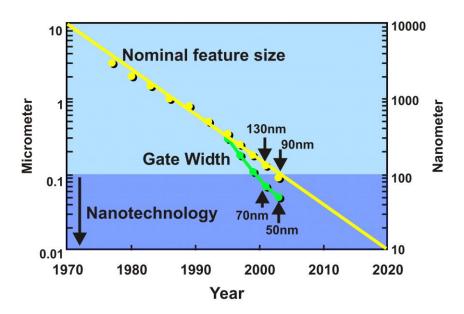

# Schnelle Evolution der IC-Technologien

Quelle: Int'l Technology Roadmap for Semiconductors ITRS

CMOS-Skalierung

### Digitalentwurf am Scheideweg?

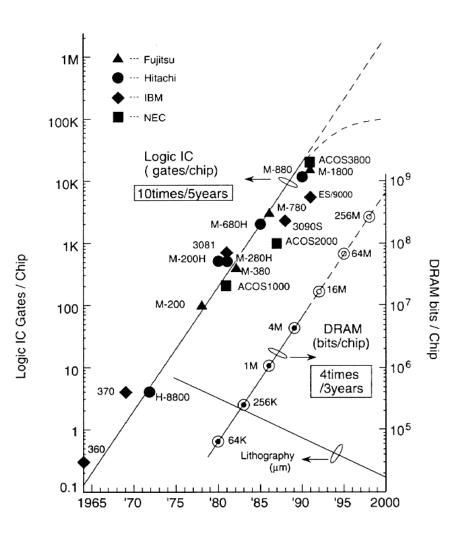

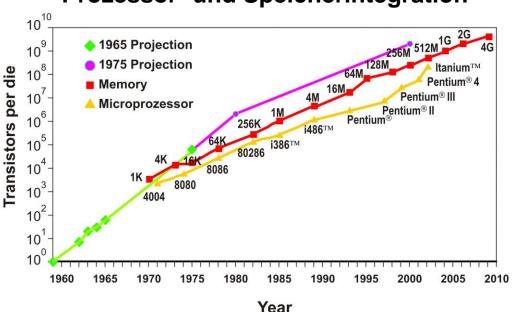

# Technologie Evolution: Integrationsdichte

#### **Moore's Gesetz**

- Die Komplexität von Speicherchips und Mikroprozessoren wuchs exponentiell

- Es war genau diese Abbildung, die Moore vorhersagte

- Moore's Law: Integrationsdichte verdoppelt sich alle 18 Monate

### Mikroelektronik: Skalierung, Verlustleistung und Kosten

#### **Prozessor- und Speicherintegration**

Prozessor- und Speicherintegrationsdichten im Vergleich zu Moore's Gesetz

(Quelle: International Technology Roadmap for Semiconductors ITRS)

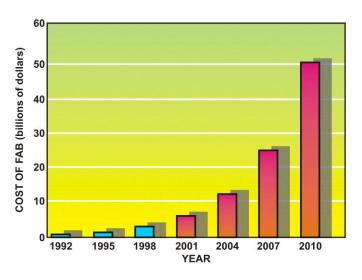

### Kostenentwicklung

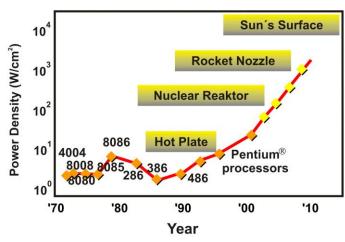

#### Verlustleistungsentwicklung

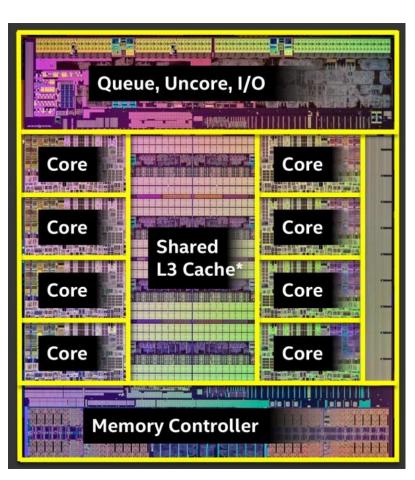

# Intel's Prozessorlösung: Core i7

### 22 nm Intel Core i7-5960X

- 8 Cores, 16 Threads

- 3.2 Milliarden Transistoren

- 355 mm<sup>2</sup> Die-Size

- 20 MB On-Chip L3-Cache

- 3.5 GHz Turbo Boost

Quelle: Jason Stinson (Intel), 2014